Without productivity gains, design size and complexity would face huge headwinds. Those gains come from a diverse set of improvements.

Brian Bailey, Semiconductor Engineering

September 24, 2020

Designs have become larger and more complex and yet design time has shortened, but team sizes remain essentially flat. Does this show that productivity is keeping pace with complexity for everyone?

The answer appears to be yes, at least for now, for a multitude of reasons. More design and IP reuse is using more and larger IP blocks and subsystems. In addition, the tools are improving, and more feedback loops are making continuous improvements.

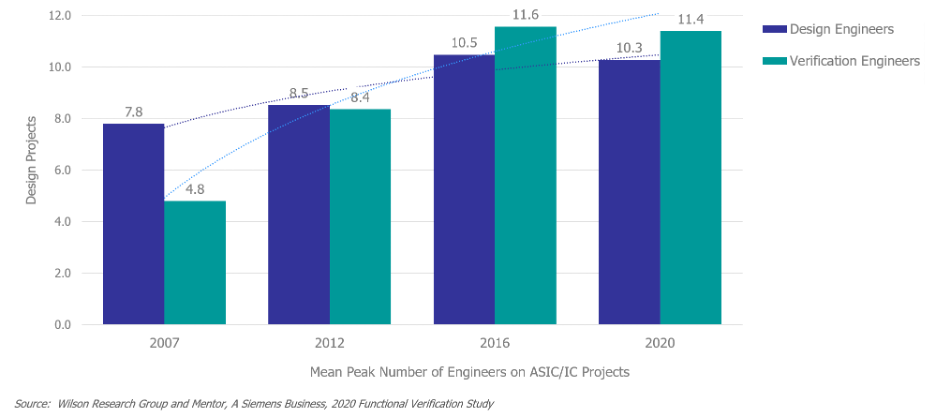

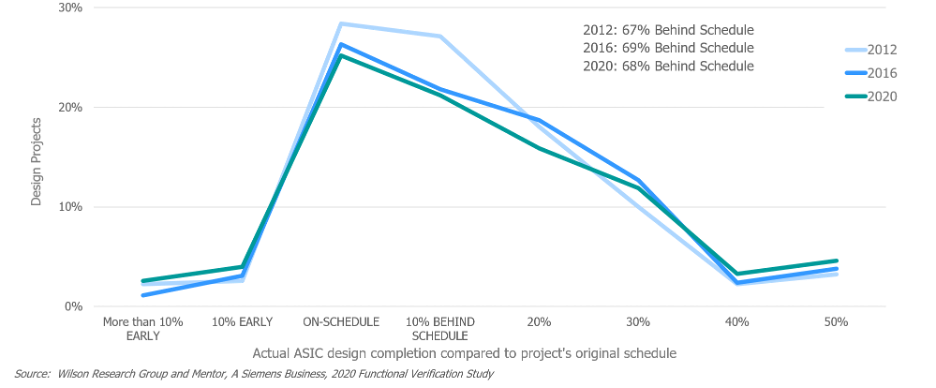

Wilson Research and Mentor, a Siemens Business, just published the results of a verification survey1 for 2020. It tracks team sizes (figure 1), schedules, and the ability for teams to meet those schedules (figure 2).

Source: Mentor, A Siemens Business

Source: Mentor, a Siemens Business

The data indicates that productivity has approximately matched the increase in complexity of designs since 2016. There appears to be a slight drop in the ability to meet schedules, but nothing statistically outside of the margin of error. How are teams managing to do this and where are the productivity gains coming from?

[…]

An improvement in verification IP has also helped. “The time spent on verification is not expanding noticeably,” says Bipul Talukdar, director of applications engineering for SmartDV in North America. “Any number of factors could contribute to that stabilization, including availability of new tools and methodologies, such as synthesizable transactors that reduce the lag time when moving between simulation and emulation. Commercial viability of FPGA prototyping enables more verification since it is faster than simulation. Perhaps the biggest reason is the more widely available verification IP from third-party vendors, so verification engineers don’t need to develop it themselves.”

[…]

Conclusion

Through a combination of design practices, verification methodologies, improved tools, and tightening or creating feedback loops within the flows, productivity is keeping up with design size – even for many of the largest chips. Those increases in productivity enable the next increase in complexity. They have to go hand in hand. Otherwise, the process would stall. Designs on older technologies often reap the rewards.

1The study included responses from 1,492 people, about half of which were involved in ASIC and IC design. The margin of error for the survey is +/- 3%.