Blog by Erik Panu, Chief Business Officer, SmartDV

There are a lot of perks to living in the Bay Area—mild weather, diverse culture, and beautiful nature, just to name a few—but this week gave me the opportunity to take advantage of one in particular: regular attendance at a wide variety of semiconductor industry conferences.

Temporarily trading the serenity of the Santa Cruz Mountains for the energy of Silicon Valley, I spent last Tuesday and Wednesday at the annual RISC-V Summit in Santa Clara. In case you weren’t able to attend, I’d like to share a few of my top takeaways from what I found to be an edifying and even eye-opening event.

Day 1: Tuesday, November 7th

I devoted much of Day 1 to attending the keynotes and sessions. Here are some of the highlights:

1. Calista Redmond, CEO, RISC-V International

Calista shared RISC-V International’s vision clearly and succinctly: “This is a wholistic business strategy.” RISC-V International aims to enable its constituents to elevate industry leadership, build a strategic network, achieve business ROI, and gain technical advantage.

Calista went on to divulge the latest industry analyst findings on RISC-V, among which I found the following points to be particularly salient:

- RISC-V will be in more than 16 billion (yes, “billion” with a ‘b’!) SoCs by 2030

- RISC-V stands to capture 27% of automotive AI acceleration by 2030

- RISC-V will command 28% of the IoT market by 2025, with a projected volume of 20 billion (there’s that ‘b’ again!) IoT cores shipped by 2028

All of this points to a vibrant, thriving, and growing RISC-V ecosystem, the landscape of which you can explore here in a dynamically-generated digital viewer.

Balaji Baktha, Founder & CEO, Ventana Micro Systems

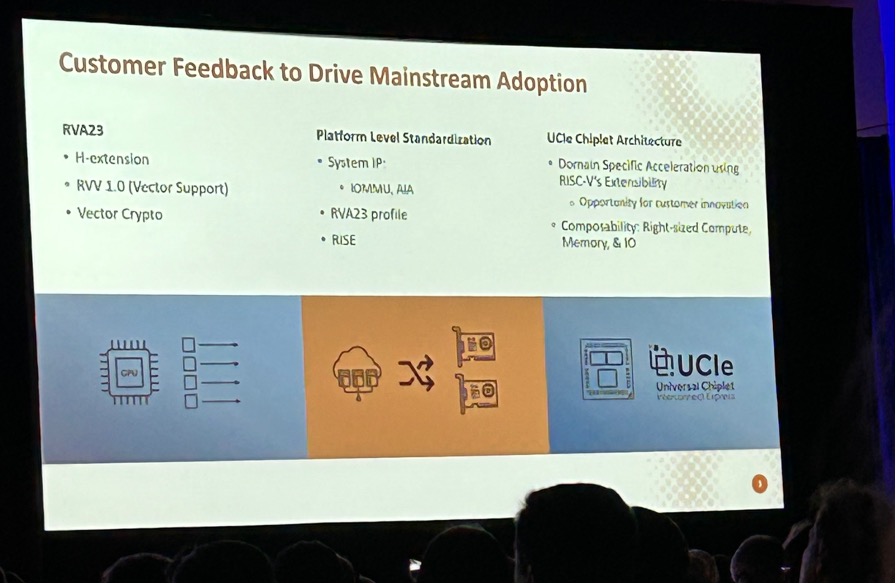

Two points Balaji made during his talk caught my attention. He stressed that “RISC-V architecture fits chiplet architecture perfectly,” indicating that both boats would continue to rise on the same flow tide we’re currently seeing. Balaji also alluded to Google’s recent announcement “that it will be treating RISC-V as one of the major ISAs in the client device market.”

As the slide above indicates, the clear moral of the story is that customer adoption is making RISC-V mainstream. It is no longer just a fringe choice: RISC-V now drives process conversations because it offers new capabilities and flexibility that single-vendor solutions, no matter their ecosystem, do not.

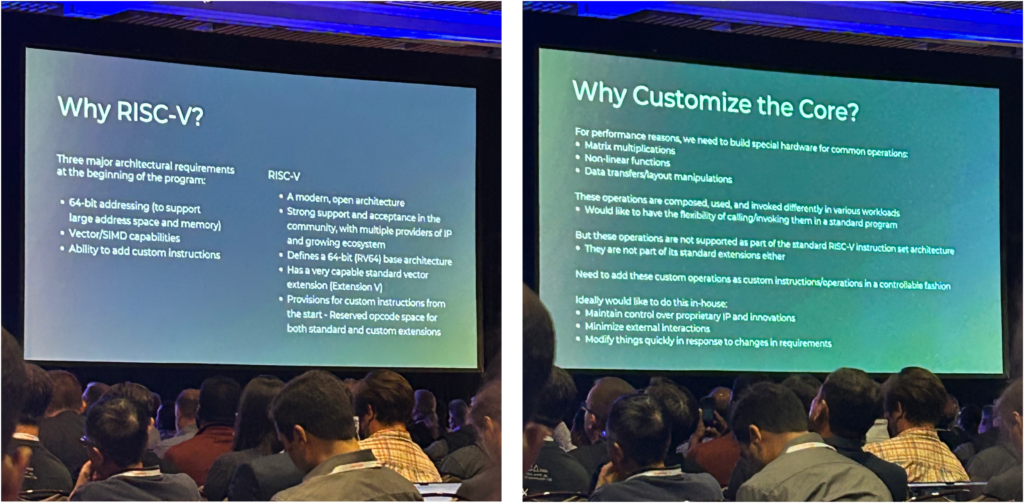

Prahlad Venkatapuram, Senior Director of Engineering, Meta

Prahlad highlighted RISC-V’s suitability for a number of major architectural requirements. He went on to stress the intense desirability of one of RISC-V’s key differentiators: customization. Custom instructions, extensions, and operations can allow for greater performance and other optimizations, affording chip designers a significant competitive edge.

For IP providers, Prahlad’s presentation offered a lot to be excited about—if the provider is willing to customize, that is! Simply put: bus IP providers will need to customize their IP to accommodate RISC-V users as they, in turn, customize the RISC-V processors they’re using in their designs. Prahlad actually bemoaned the lack of extensive customization capability in existing IP offerings as a major challenge in hardware and architecture. Seamless IP integration and interoperability from different vendors ranked near the top of his wish list, along with a sophisticated debug environment. Prahlad also underscored the critical need for:

- A robust ecosystem to support the commercial success of RISC-V

- Standard specifications for customization, with encoding space earmarked for custom instructions

- Peripheral IP tested with RISC-V cores

On that third point, a prime example would be the suite of SmartDV peripheral IP currently offered as a companion to Codasip’s processors—more on that later. 🙂 All shameless self-promotion aside: as RISC-V adoption further expands, the need for customizable IP from trusted suppliers will only continue to grow. IP suppliers will need to keep pace or be left behind.

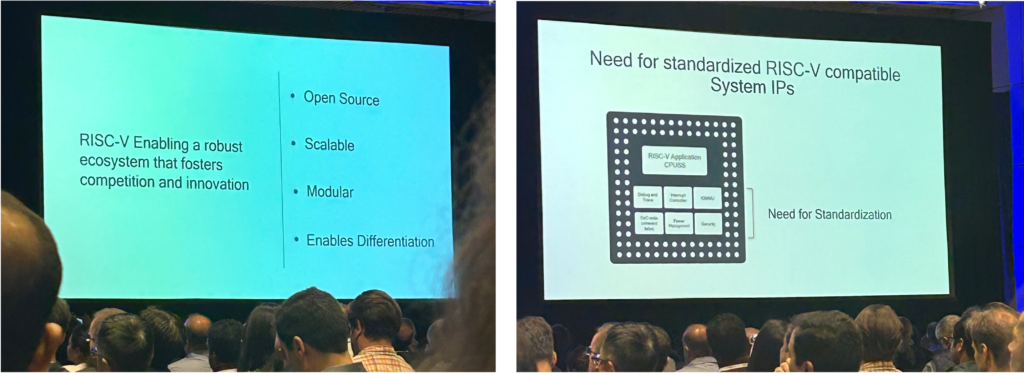

Ziad Asfhar, Senior Vice President of Product Management, Qualcomm

By the time Ziad took the stage, two clear themes were coming to the fore, as evidenced by these two slides:

Here are some of my favorite soundbites from Ziad’s talk, which, I think, speak for themselves:

- “$700B addressable edge device market in next decade”

- “Qualcomm shipped 650 million devices in 2022”

- “The part I am really focused on is the customization [because] it allows us to focus on the consumer’s experience”

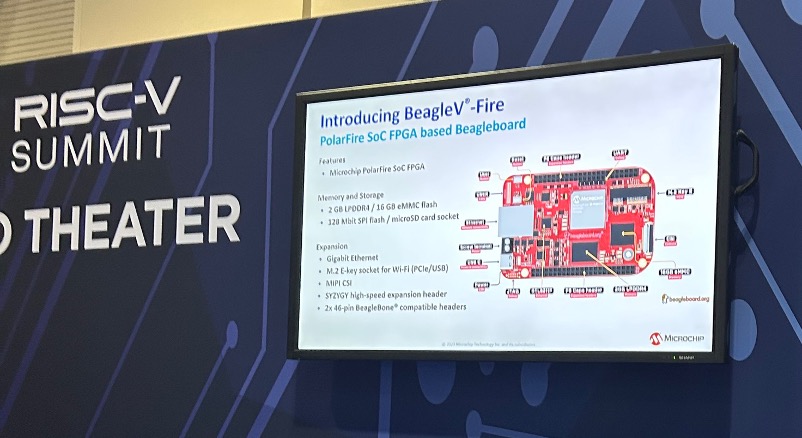

Later in the day, I stopped by the RISC-V Demo Theater to catch the presentation from Microchip about their new BeagleV-Fire, a PolarFire SoC FPGA based Beagleboard.

Day 2: Wednesday, November 8th

For Day 2, I shifted my focus to the RISC-V ecosystem being showcased at the Summit. Over the past few years, SmartDV has carved out a niche here through strategic IP partnerships with Codasip, NSI-TEXE, and other leading RISC-V players. Codasip was a platinum sponsor of this year’s Summit, with both an exhibit and content all over the technical program, so it was a great chance for me to further strengthen our ties with them.

I started the morning with Codasip CEO Ron Black’s keynote address on processor security, during which he offered exciting details on Codasip’s industry-first commercial implementation of CHERI.

If you’re not familiar, CHERI—short for Capability Hardware Enhanced RISC Instructions—is an ISA extension developed by the University of Cambridge to enable fine-grained memory protection. (You can learn more about CHERI here and read Codasip’s announcement here.) SmartDV applauds this exciting news from our partner, Codasip, and we look forward to supporting the further opportunities we know it will fuel!

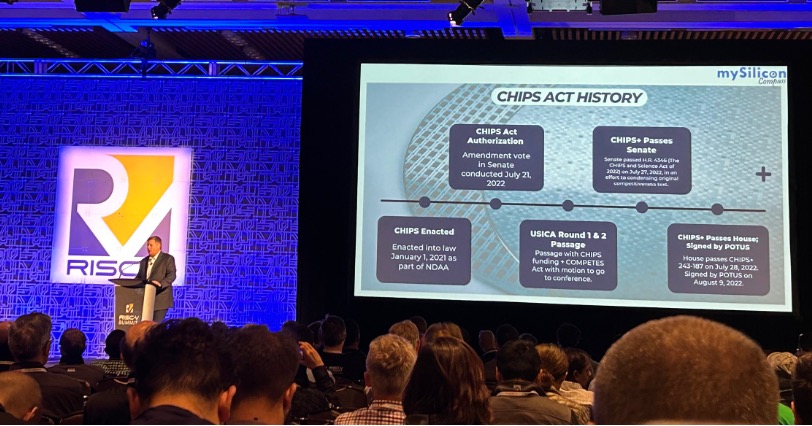

Also notable and interesting during the morning session was the keynote from the Honorable Ian Steff; Former Assistant Secretary of Commerce and President & CEO, mySilicon Compass.

There was a great deal to absorb here regarding the CHIPS Act, with Ian first delving into its history before offering an overview of the current and ongoing federally-backed provisions of the CHIPS for America Fund (FY 2022–2026)—to the tune of tens of billions of dollars. There is abundant opportunity here for those who wish to seize it!

I spent the latter part of Day 2 in the RISC-V Summit Exhibit Hall. I visited Codasip’s booth to spend some quality time with their team, many of whom had traveled from the company’s various offices in Europe to attend the conference. Here I am, mugging for the camera with VP Strategy & Ecosystem Mike Eftimakis.

Mike and I have gotten to know each other this year through the formation of the Codasip/SmartDV partnership, which I mentioned earlier in this blog, and have greatly enjoyed working together to refine it and keep it moving forward.

While at Codasip’s booth, I took the opportunity to check out their latest Custom Compute technical demo, featuring the suite of SmartDV peripheral IP that is included in our one-stop-IP-licensing partnership.

We are thrilled to see customers around the world responding enthusiastically to this joint offering. There was quite a crowd at the booth to see the demo, so it seems that the excitement continues! I’m particularly gratified that we are able to smooth the way for our users’ design and verification teams when it comes to sourcing a RISC-V processor and companion peripheral IP under a single license agreement. By working closely together—through deep R&D collaboration, advance testing, and successful proofs-of-concept—Codasip and SmartDV are taking the guesswork out of RISC-V and IP integration for our customers.

There were a couple of other themes that bubbled to the surface during Day 2 of the RISC-V Summit.

First: as standards emerge in the RISC-V ecosystem, software drivers will come to the fore as a key need that users will look to IP vendors to provide. There will be added complexities where customization is involved, so it will be up to IP vendors to work closely with their users to chart a sensible course forward. The second theme

The second theme was verification. As with any other processor platform, RISC-V will demand strong standards verification from SoC and systems providers operating in this space. Imperas and others are starting down this path, but the ecosystem as a whole is still finding its way in this realm.

In Summary

As was made abundantly clear in this week’s visionary presentations at the RISC-V Summit (and further driven home by the 1000+ strong attendance), RISC-V isn’t going anywhere—in fact, it looks to be well on its way to ubiquity.

So, what’s the major takeaway?

RISC-V processors offer chip designers unprecedented flexibility and the opportunity to tailor their products to the exacting needs of end users. IP providers, in turn, must be prepared to support changes to their interfaces to meet users’ evolving needs. In this world of choice and flexibility, IP customization is no longer niche or optional: it is vitally important.

SmartDV’s customizable design IP and VIP cores make ideal complements to RISC-V processors because of our willingness toward, and deep experience with, IP customization—and even the creation of completely bespoke IP. Gone are the days of being locked into an IP supplier’s rigid feature sets or gate counts. Sourcing design IP and VIP from SmartDV means gaining a trusted IP partner whose expert engineers will become an extension of your own team and work alongside you to achieve the precise functionality and PPA you need to succeed.

Ready to get started with RISC-V processors and customized IP? SmartDV can help! Learn more at https://smartdvtech.com/services_customized_ip/.

About Erik Panu

Erik Panu leads the North American and European businesses for SmartDV, heading a team of sales, marketing, and technical professionals who support customer engagements, press/media, events, and company operations. Erik’s past career experiences—as general manager of the Cadence IP Group and head of business at AI startups including BabbleLabs—position him to scale SmartDV’s business to better and more broadly provide value to SmartDV’s customers. Erik lives with his family in the Santa Cruz Mountains of California, right at the edge of Silicon Valley.