Mike Gianfagna, Semiconductor Engineering

April 21, 2020

In the technology industry, we’re all used to the hype about the latest and greatest. Semiconductor IP participates in the over-drive news cycle from time to time as well. So, when I see a company that has real, solid credentials but has resisted the temptation to over-hype, it gets my attention. I had an experience like this recently relative to SmartDV.

The company is a new sponsor for SemiWiki, and I spent some time recently speaking with Barry Lazow, their vice president of worldwide sales and marketing. Barry has been doing high technology sales work for quite a while, all the way back to VLSI Technology, arguably one of the true pioneering companies in semiconductor. I took the opportunity to probe Barry about the story behind SmartDV.

What I found was, in a word, breathtaking. First of all, the company is self-funded. No VC commitments, no need to waiver from their core focus, which is stated as “being #1 in verification and design IP,” a lofty goal. Barry describes the company as a family business, with the founding team of chip design and verification experts still in place after 12 years. The company’s development team of over 250 people is located in Bangalore, India.

They maintain a three-shift operation there to ensure worldwide coverage for customer support, which they earn high marks for from their customers. Doing centralized support this way can be challenging and it seems SmartDV has figured out how to do it right. Speaking of customers, Barry explained that more than 100 companies worldwide rely on SmartDV’s products, including seven of the top ten worldwide semiconductor companies.

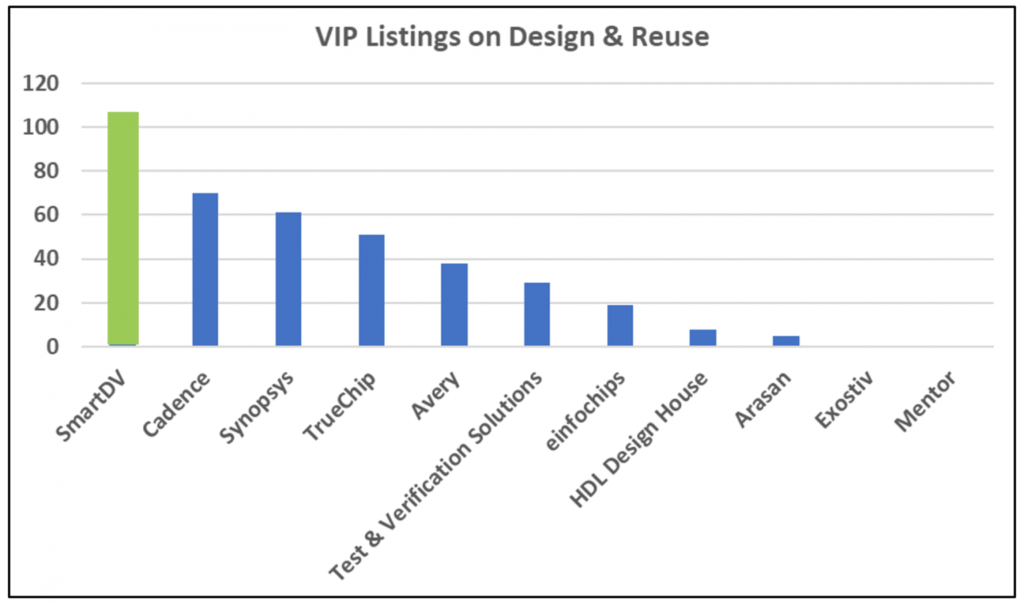

So, what does SmartDV offer? Their focus is on verification IP (VIP) and design IP, with over 400 titles in their portfolio. The figure below drives home the point about being #1.

In the VIP area, the SmartDV portfolio is quite robust. It includes models for simulation, emulation (synthesizable transactors (SimXL) for accelerating emulation), assertion-based VIP (formal verification), FPGA prototyping and verification (with a supplied LINUX Perl driver), post-silicon verification and a visual debugger called SmartViP debug for rapid analysis of protocol issues. Probing a bit more, SmartDV’s VIP has native support for UVM, System Verilog, VMM, OVM, Vera, Verilog and SystemC/TLM. Quite a list. Each VIP also includes a compliance test suite and a functional coverage model, which is not always the case with VIP.

Barry pointed out another key attribute of this VIP, the ability to seamlessly transition from simulation to emulation. I have plenty of stories of that transition taking many months. I recall the term “design for emulation”. You probably have some of your own stories. An easy transition to emulation is a big deal. All the major emulators are supported of course. Another statistic Barry shared was from his customers, who report compile times for SmartDV VIP being 2-3X faster than the competition. Impressive.

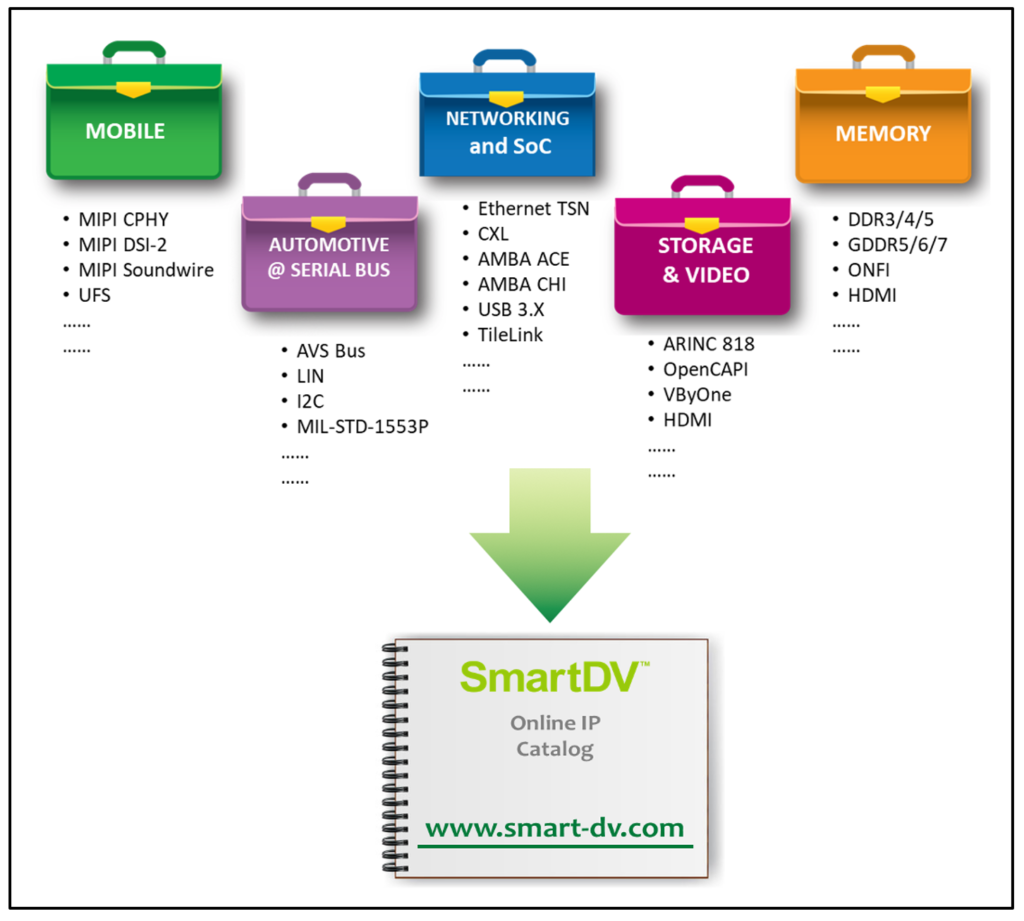

In the design IP area, SmartDV offers synthesizable RTL in Verilog or VHDL to cover popular interfaces such as MIPI, AMBA, PCI, CAN, RapidIO and so on. After our tour of IP products, just when I thought I had heard all the juicy stuff, Barry gave me one more tidbit – perhaps the key secret of SmartDV’s success. SmartDV’s products are typically sold as soft, compilable IP. Nothing really new there. What is new is that ALL of their products are built with a proprietary compiler technology which utilizes a proprietary language that drives the process.

This has some significant implications. Let’s start with the myth of standard, off-the-shelf IP. We all know that does happen sometimes, but often there are tweaks needed to use an IP block effectively. That usually translates into additional manpower at the vendor to implement the tweaks and associated delivery delays. This is not the case at SmartDV. Thanks to their proprietary compiler, the company can implement modifications in days. This is one of the reasons for their high marks in customer support. Barry explained that an entirely new piece of VIP can typically be done in 4-6 weeks, but typical customization is done in 1-2 weeks. This allows the company to be first to market supporting virtually all new and emerging protocols, as depicted in the figure below. As an example, SmartDV was first to market with VIP to support TileLink, the RISC-V interconnect fabric.

SmartDV also provides verification services – they are a one-stop shop for a huge part of a project’s verification needs You can learn more about this quiet, but potent company at the SmartDV website. If you have verification or design IP needs for your next project, I strongly recommend you start there.